# APPLICATION NOTE 26

POWER OPERATIONAL AMPLIFIER HTTP://WWW.APEXMICROTECH.COM (800) 546-APEX (800) 546-2739

#### PARALLEL CONNECTION OF POWER OP AMPS

Power op amps can be paralleled to increase current, improve SOA (Safe-Operating-Area), or double thermal capability. While the basic topology seems simple, there are design details which require careful attention such as common-mode range considerations, stability, slew rate, and losses which can reduce efficiency and increase power dissipation.

#### **1.0 BASIC PARALLEL TOPOLOGY**

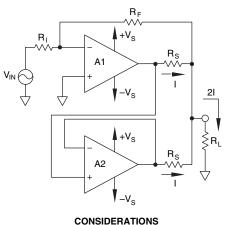

A1 in Figure 1 referred to as the master amplifier, can be configured in any form desired, inverting or non-inverting, and any gain desired. Feedback for A1, and only A1, will come from the overall output of the parallel connection. The output of each amplifier will have in series equal small-value resistors to improve current sharing characteristics. The slave amplifiers, A2 and up to An, are configured as unity gain non-inverting buffers driven from the output terminal of the master amplifier A1. Each slave's individual feedback is taken directly at its output terminal.

The idea of this connection is since each slave is a unity gain buffer, the slave outputs will match as closely as possible the output of the master. Yet with the master feedback being wrapped around the entire circuit, overall accuracy is maintained.

# $I_{LOSS} = V_{OS}/2R_S$

V<sub>LOSS</sub> = I<sub>OUT</sub>R<sub>S</sub> SLEW RATE MISMATCH WILL GIVE LARGE I<sub>CIBC</sub>

FIGURE 1. BASIC CONNECTION.

#### **2.0 LOSSES**

The output of the slaves in this configuration will not exactly match the master. Since the slaves operate at unity gain, the difference will be equal to the worst case offset of a single amplifier for two amplifiers in parallel since only the offset of the slave causes this mismatch. With more than one slave, each slave could have worst case offset in opposite directions, and in the worst case, the mismatch is twice the input offset voltage.

These offset voltages produce a drop across the current

sharing resistors and a corresponding current flow. This is current that is "lost", never appearing in the load and increasing amplifier dissipation.

Even a unity gain buffer (the slave amplifier) has phase shift making it's instantaneous output voltage different from the master amplifier, and again producing a voltage drop across the sharing resistors. If the desired signal frequency is grater than half the power bandwidth of the amplifier, the parallel connection will likely not be practical. To check a specific application, Use Power Design to find closed loop phase shift, multiply the sine of that angle times the peak output voltage to find the peak difference voltage across the sharing resistors. This current is again "lost", never appears in the load and increases amplifier heating.

#### **2.1 CURRENT SHARING RESISTOR CHOICE**

Increasing values of current sharing resistors will reduce the circulating current loss. But this improvement must be weighed against direct losses through the current sharing resistors when delivering current to the load. The challenge to the designer is to find the happy medium for Rs values. As a general rule, power amplifiers will be used with Rs values of from 0.1 ohm to 1.0 ohm.

#### **3.0 CURRENT LIMITING**

Current limit of the master should be set 20% lower than the slaves if possible, and the ultimate current limit of the overall circuit will be that limit multiplied by the total number of amplifiers. The idea here is the master current limits first, and since it provides the drive for all other amplifiers, that drive is also clipped. This insures equal sharing of all stresses during current limit.

#### **4.0 SLEW RATE CONSIDERATIONS**

Assume an initial condition where the output of the circuit in Figure 1 is resting close to the negative rail. Then apply a step function to the input of the master amplifier to drive the output positive. The output will slew as fast as the amplifier's slew rate to the positive rail. With the slave being driven from the master, the slave doesn't get its input transition until the master slews, and then the slave requires additional time to slew positive.

In the interval where the master has reached positive output and the slave is trying to catch up, there is a large difference in the output voltage of the two amplifiers developing current through the two current sharing resistors. This can be a large current equivalent to the current limit of the amplifier. That's the bad news. The good news is that it is a transient current and as such may be within transient SOA limits. But this can be difficult to prove for certain.

When in doubt, the best rule of thumb is to not use the parallel connection at greater than half the rated slew rate of the amplifiers.

#### **5.0 STABILITY CONSIDERATIONS**

For detailed information on stability, refer to Application Note 19, "Stability For Power Operational Amplifiers". All discussion here is based on the stability theory contained in Application Note 19.

#### **5.1 SLAVE STABILITY**

The most obvious problem from a stability standpoint is the unity gain buffer connection of the slaves. This configuration has the least ability to tolerate poor phase margin. Poor phase margin usually occurs as a result of excessive capacitive loading. But in the case of the PA12, the unity gain buffer connection should not be used without additional compensation. Externally compensated amplifiers should normally be compensated for unity gain and may still require additional compensated to improve slew rate and use noise gain compensation to insure stability.

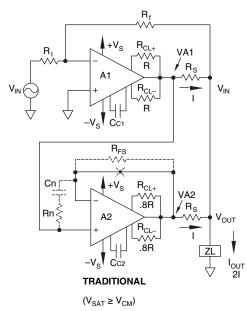

The most common way we recommend to compensate the slave is with a noise gain compensation network across the inputs to the amplifier. However, for noise gain compensation to work, there must be impedance in the feedback path. Figure 2 shows the modifications necessary to incorporate noise gain compensation.

The R<sub>FS</sub> value of Figure 2 is somewhat arbitrary, but its choice will dictate the final values of Rn and Cn. As is the general case in any op amp circuit, excessive impedance for RFs is something to be avoided. A realistic range of values for RFs is from 1 K $\Omega$  to 1 M $\Omega$  with a good starting point being 10 K $\Omega$ .

Once the value of  $R_{FS}$  is pegged, noise gain compensation should usually be set to give a noise gain of 10. This corresponds to Rn being one-tenth Rf. Cn must be found analytically according to procedures outlined in Application Note 19 after considering the effects of amplifier bode plot and additional poles resulting from capacitive loading. In many cases, selecting Cn for a corner frequency of 10KHz based on the value of Rn (Xcn = Rn@10KHz) will result in a stable circuit; although, analytical methods will maximize bandwidth in comparison to this method.

FIGURE 2. SLAVE STABILITY.

#### **5.2 MASTER STABILITY**

A1 is subject to all normal considerations for stability. If A1 is a gain of 10 or greater, its stability will be equal to that of the slave with noise gain compensation described above. At gains below 10, the optimum noise gain will be a gain of 10 to match the slaves.

### 6.0 COMMON MODE CONSIDERATIONS

The unity gain buffer configuration must be able to accept inputs equal to the maximum output swing of the master. This will be a problem with MOST amplifiers. Light loads make the situation worse. Both the output voltage swing and the common mode voltage range specifications are given as volts from the supply rail. Read the output voltage swing from the typical graph at the lowest possible current the amplifier will be required to drive when the input signal calls for saturation. Read the common mode voltage specification from the specification table in the MIN column. For the parallel configuration to work without special circuitry, the output voltage swing must be at least as large as the common mode voltage specification.

The PA02 does not lend itself to parallel connection. Negative inputs which get closer than 6 volts of the negative supply rail can cause output polarity reversals which can be catastrophic in the parallel connection.

## 6.1 OVERCOMING COMMON MODE RESTRICTIONS

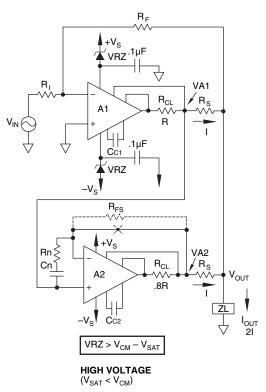

A method most useful with high voltage amplifiers where currents are low, is to simply use zener diodes in series with the supply line to the master amplifier as shown in Figure 3A. These drop the master supply low enough to restrict its output swing to be within the common-mode range of the slaves. Determine wattage ratings based on expected load + quiescent current flow.

FIGURE 3A. OVERCOMING COMMON MODE RESTRICTIONS.

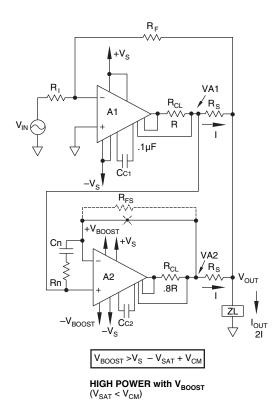

The PA04 and PA05 present another opportunity to overcome common-mode limitations by taking advantage of their boost pins. Originally incorporated to improve output voltage swing, we effectively increase common-mode range by increasing front-end supply voltages. A boost of at least 5 volts will be adequate to overcome this limitation. Figure 3B elaborates on this connection.

FIGURE 3B. OVERCOMING COMMON MODE RESTRICTIONS.

Other methods include operating slaves on slightly higher voltages than the master. This is what is accomplished with the zeners described previously, but is not easily applied to high current power amplifiers unless they have boost voltage provisions. In such cases the zeners can be included in series with the Vboost pins of the master amplifier.

It may seem possible to attenuate the output of the master and set the slaves up with corresponding gain, but it will be found that unless very strict matching requirements of the associated resistors are met, extremely large circulating currents will flow.

### **7.0 BRIDGE CIRCUITS**

The master-slave combination once realized and taken as a whole, comprises one effective op amp. Treated this way, incorporation into a bridge circuit is simply a matter of using an inverting unity gain configuration on the slave side of the bridge (note that the slave of the parallel combination and the slave side of a bridge are two different things). Bridge techniques are discussed in detail in Application Note 20, "Bridge Operation".

#### **8.0 SINGLE SUPPLY**

There are no unique considerations concerning single supply except those described in Application Note 21, "Single Supply Operation". Again, as in the bridge, treat the parallel combination as a single op amp.